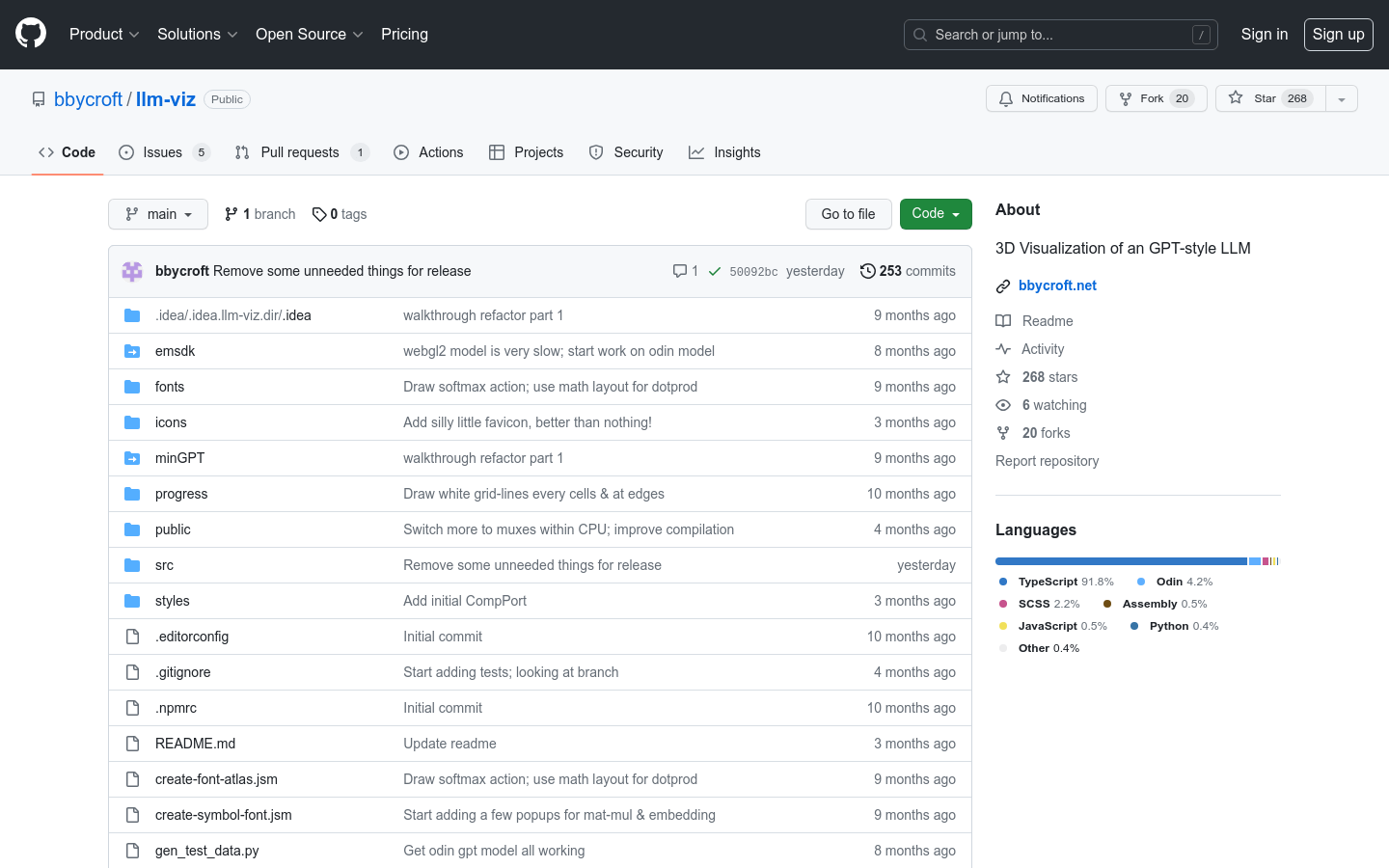

LLM Visualization

LLM Visualization:3D Visualization of GPT-Style LLMs

Tags:AI model3D AI model AI Tools URL Directory CPU Simulation Digital Circuit GPT Network Model Open Source Standard PicksProject Overview

The LLM Visualization project offers a unique 3D modeling capability for GPT-style neural networks. This visualization tool is based on the network architecture utilized in OpenAI’s GPT-2, GPT-3 (and potentially future iterations like GPT-4). The initial demonstration model provided is a simplified network designed to sort a list of letters (A, B, and C), drawn from Andrej Karpathy’s minGPT implementation. While this serves as an introductory example, the system is scalable and capable of rendering networks of various sizes. Note that for smaller GPT-2 models, the weights are not downloaded due to their relatively modest size (typically in the hundreds of megabytes). This approach ensures efficient resource management while maintaining functionality.

LLM Visualization Capabilities

- Network Topology Display: Renders detailed 3D models of GPT-style networks, providing a visual representation of their structure and connections.

- Scalability: Supports visualization of networks across different sizes, from small demonstration models to larger architectures.

CPU Simulation Features

Beyond its primary focus on neural network visualization, the project also incorporates a CPU simulation module designed for 2D digital circuit analysis. The system includes:

Simulation Editor and Analysis Tools

- 2D Digital Circuit Runtime: Enables the operation and monitoring of digital circuits in a 2D environment.

- Interactive Editing Capabilities: Offers a comprehensive editor for designing and modifying digital circuits, allowing users to experiment with different configurations and behaviors.

Digital Circuit Demonstrations

The simulation module is designed to educate users about various aspects of CPU design and operation. Key areas of focus include:

Instruction Set Architecture (ISA) and Components

- Building a Simple RISC-V CPU: Demonstrates the foundational principles of constructing a basic RISC-V instruction set architecture.

- <strong/Gate-Level Construction: Breaks down the process of building components at the gate level, including:

- Instruction decoding mechanisms

- Arithmetic Logic Unit (ALU) implementation

- Addition operations and logic circuits

Advanced CPU Concepts

- Pipelining: Explains the concept of instruction pipelines, including different levels of pipelining complexity.

- Caching Mechanisms: Illustrates how cache memories operate at various levels within a processor design.

Target Audience and Applications

Primary Users

The project is designed for:

- Educators: Teaching the inner workings of GPT-style networks and digital circuitry.

- Researchers: As a visualization tool for studying large language models and CPU architectures.

- Students: Learning about neural network structures and CPU design principles through interactive simulations.

Potential Use Cases

- Educational Demonstrations: Visualizing the architecture and operations of GPT-style networks in a classroom setting.

- Circuit Simulation: Using the digital circuit simulator to teach fundamental concepts like instruction decoding, arithmetic operations, and pipeline stages.

- Research Support: Providing visualization tools for academic research on neural network architectures and CPU design.

System Features

- 3D Network Visualization: Capable of rendering complex GPT-style networks in three dimensions, offering an intuitive view of their structure and connections.

- Scalability: The system accommodates networks of varying sizes, making it adaptable to different use cases and research needs.

- Digital Circuit Simulation: Offers a comprehensive environment for designing, editing, and analyzing 2D digital circuits, with an emphasis on educational and instructional applications.

This project combines cutting-edge visualization techniques with interactive simulation tools, making it a valuable resource for education, research, and professional development in the fields of artificial intelligence and computer architecture.